I have been meaning to write a SystemVerilog Assertions (SVA) Cheat Sheet for about 5 years. It was one of those things that I kept putting off because I didn’t know how I wanted to approach it. There are many features in SVAs and most of them aren’t used much. I couldn’t get myself to list all the features of the IEEE1800-2012 standard in a condensed format, because it would serve me no purpose. The simple assertions are the easiest to understand, easiest to get right and they simulate the fastest, so a cheat sheet should focus on that.

I created a SystemVerilog Assertions Checklist in the spring of 2015 and thought that it would be useful to combine the checklist and a cheat sheet into a useful whole. I have been using this combination since and tested it on a few coworkers. So far it appears to be useful. I think that it would be a good tool for relatively inexperienced SVA practitioners as it makes low level verification a more mechanical than intellectual effort. Please let me know if this is the case or if it falls short of that.

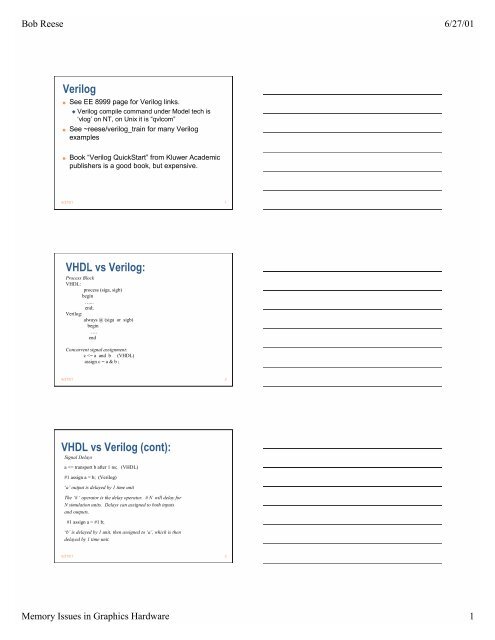

Cheat sheet for Verilog `timescale 1ns / 1ps module ModuleName #(parameter PNAME = 4, localparam LPNAME = CPNAME.1) // comment ( input wire clk, input wire reset, input wire PNAME-1:0din, output wire LPNAME-1:0dout ); endmodule. The intention of this document is to get your familiar programming and using the Fipsy FPGA using a pre-built example – Blinky. Pathfinder rpg books pdf download free. The steps below will have you download the code, install the development tool, work with a project file, and upload the design to the FPGA.

Verilog Hdl Pdf

- NOTE: This is a work in progress, please let us know via issue/gitter/email if you'd like to see anything added to this. This is inspired by the chisel cheatsheet and will be rendered in a similar single page layout soon. M.Bit: boolean value; m.VCC, m.GND: boolean literals; Bits and Integers. M.BitsN: length N bit vector with bitwise logical operators defined.

- Verilog Cheat Sheet (version 0.8) for CS552 - Spring 2013 1 Developed by: Vinay Gangadhar, Cherin Joseph & Prof. Karthikeyan Sankaralingam Email (karu@cs.wisc.edu) things to add to cheat sheet. 1 course point (on 100) for each idea accepted; cumulative no more than 5 for a student. Email (karu@cs.wisc.edu) any bugs/typos you find. 1 course point (on 100) for genuine bugs; cumulative.

- Systemverilog.io is a resource that explains concepts related to ASIC, FPGA and system design. It covers a wide variety of topics such as understanding the basics of DDR4, SytemVerilog language constructs, UVM, Formal Verification, Signal Integrity and Physical Design.

Systemverilog Operators

The assertions in the checklist are all valid SystemVerilog 2005. They should work in both simulators and in formal verification engines, but the with an emphasis on simulation performance. Download it, print it out and put it next to you on your desk. Happy coding: